#### 5821 thru 5823 Bimos II 8-BIT SERIAL-INPUT, LATCHED DRIVERS

TWDICAT INDITE OTDOTTEC

## 410.068

# 5821 THRU 5823

#### Bimos II 8-BIT SERIAL-INPUT, LATCHED DRIVERS

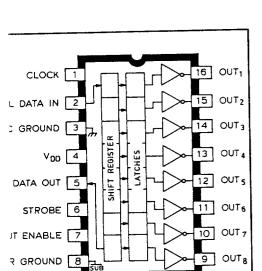

A merged combination of bipolar and MOS technology gives these devices an interface flexibility beyond the reach of standard logic buffers and power driver arrays. The three devices in this series each have an eight-bit CMOS shift register and CMOS control circuitry, eight CMOS data latches, and eight bipolar current-sinking Darlington output drivers. Except for maximum driver output voltage ratings, the UCN5821A, UCN5822A, and UCN5823A are identical.

BiMOS II devices have much higher data-input rates than the original BiMOS circuits. With a 5 V logic supply, they will typically operate at better than 5 MHz. With a 12 V supply, significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS and NMOS logic levels. TTL circuits may require the use of appropriate pull-up resistors. By using the serial data output, the drivers can be cascaded for interface applications requiring additional drive lines.

- 3.3 MHz Minimum Data Input Rate

- CMOS, NMOS, TTL Compatible

- Internal Pull-Down Resistors

- Low-Power CMOS Logic & Latches

- High-Voltage Current-Sink Outputs

- 16-Pin Dual In-Line Plastic Package

Dwg No PP-026

-20°C to +85°C

#### BSOLUTE MAXIMUM RATINGS at 25°C Free-Air Temperature

| out Voltage, V <sub>OUT</sub>          |

|----------------------------------------|

| (UCN5821A)                             |

| (UCN5822A)                             |

| (UCN5823A)100 V                        |

| c Supply Voltage, V <sub>DD</sub> 15 V |

| it Voltage Range,                      |

| $V_{IN}$ -0.3 V to $V_{DD}$ + 0.3 V    |

| tinuous Output Current,                |

| I <sub>OUT</sub> 500 mA                |

| kage Power Dissipation,                |

| P <sub>D</sub>                         |

| erating Temperature Range,             |

#### 21 thru 5823 Mos II 8-bit serial-input, latched drivers

#### TRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ , $V_{DD} = 5$ V, (unless otherwise specified).

|                    |                      | Applicable |                                                            | Limits      |      |       |  |  |

|--------------------|----------------------|------------|------------------------------------------------------------|-------------|------|-------|--|--|

| ecteristic         | Symbol               | Devices    | Test Conditions                                            | Min.        | Max. | Units |  |  |

| it Leakage Current | I <sub>CEX</sub>     | UCN5821A   | V <sub>OUT</sub> = 50 V                                    | _           | 50   | μА    |  |  |

|                    |                      |            | V <sub>OUT</sub> = 50 V, T <sub>A</sub> = +70°C            | _           | 100  | μА    |  |  |

|                    |                      | UCN5822A   | V <sub>OUT</sub> = 80 V                                    |             | 50   | μА    |  |  |

|                    |                      |            | V <sub>OUT</sub> = 80 V, T <sub>A</sub> = +70°C            | _           | 100  | μА    |  |  |

|                    |                      | UCN5823A   | V <sub>OUT</sub> = 100 V                                   | _           | 50   | μА    |  |  |

|                    |                      |            | V <sub>OUT</sub> = 100 V, T <sub>A</sub> = +70°C           | <del></del> | 100  | μA    |  |  |

| tor-Emitter        | V <sub>CE(SAT)</sub> | ALL        | I <sub>OUT</sub> = 100 mA                                  |             | 1.1  | ٧     |  |  |

| ation Voltage      |                      |            | I <sub>OUT</sub> = 200 mA                                  |             | 1.3  | ٧     |  |  |

|                    |                      |            | I <sub>OUT</sub> = 350 mA, V <sub>DD</sub> = 7.0 V         |             | 1.6  | ٧     |  |  |

| Voltage            | V <sub>IN(0)</sub>   | ALL        | -                                                          | _           | 0.8  | ٧     |  |  |

|                    | V <sub>IN(1)</sub>   | ALL        | V <sub>DD</sub> = 12 V                                     | 10.5        | _    | ٧     |  |  |

|                    |                      |            | V <sub>DD</sub> = 10 V                                     | 8.5         | _    | V     |  |  |

|                    |                      |            | V <sub>DD</sub> = 5.0 V                                    | 3.5         | _    | V     |  |  |

| Resistance         | R <sub>IN</sub>      | ALL        | V <sub>DD</sub> = 12 V                                     | 50          | _    | kΩ    |  |  |

|                    |                      | •          | V <sub>DD</sub> = 10 V                                     | 50          |      | kΩ    |  |  |

|                    |                      |            | V <sub>DD</sub> = 5.0 V                                    | 50          | _    | kΩ    |  |  |

| y Current          | I <sub>DD(ON)</sub>  | ALL        | One Driver ON, V <sub>DD</sub> = 12 V                      | _           | 4.5  | mA    |  |  |

|                    |                      |            | One Driver ON, V <sub>DD</sub> = 10 V                      | _           | 3.9  | mA    |  |  |

|                    |                      |            | One Driver ON, V <sub>DD</sub> = 5.0 V                     | _           | 2.4  | mA    |  |  |

|                    | I <sub>DD(OFF)</sub> | ALL        | V <sub>DD</sub> = 5.0 V, All Drivers OFF, All Inputs = 0 V | _           | 1.6  | mA    |  |  |

|                    |                      |            | V <sub>DD</sub> = 12 V, All Drivers OFF, All Inputs = 0 V  | _           | 2.9  | mA    |  |  |

#### 5821 thru 5823 Bimos II 8-BIT SERIAL-INPUT, LATCHED DRIVERS

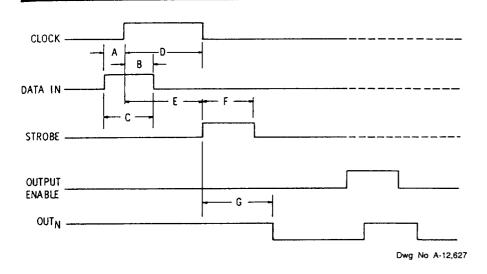

### TIMING CONDITIONS ( $V_{DD}$ = 5.0 V, $T_A$ = +25°C, Logic Levels are $V_{DD}$ and Ground)

Serial Data present at the input is transferred to the shift register on the logic "0" to logic "1" transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.

Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the ENABLE input be high during serial data entry.

When the ENABLE input is high, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the ENABLE input low, the outputs are controlled by the state of the latches.

#### TRUTH TABLE

| Serial        |       | Shift Register Contents |                |                |  |                | Serial                   |                | Latch Contents |                |        |                | _                | Output Contents |                |                |                |                |                |

|---------------|-------|-------------------------|----------------|----------------|--|----------------|--------------------------|----------------|----------------|----------------|--------|----------------|------------------|-----------------|----------------|----------------|----------------|----------------|----------------|

| Data<br>Input | Clock | l,                      | l <sub>2</sub> | l <sub>3</sub> |  | I <sub>8</sub> | Data Strobe Output Input | l <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> | •••••• | I <sub>8</sub> | Output<br>Enable | l,              | l <sub>2</sub> | l <sub>3</sub> | ************   | I <sub>8</sub> |                |

| Н             | 7     | Н                       | R,             | R <sub>2</sub> |  | R <sub>7</sub> | R <sub>7</sub>           |                |                |                |        |                |                  |                 |                |                |                |                |                |

| L             | 7     | L                       | R,             | R <sub>2</sub> |  | R <sub>7</sub> | R <sub>7</sub>           |                |                |                |        |                |                  |                 |                |                |                |                |                |

| Х             | l     | R,                      | R <sub>2</sub> | R <sub>3</sub> |  | R <sub>8</sub> | R <sub>8</sub>           |                |                |                |        |                |                  |                 |                |                |                |                |                |

|               |       | Х                       | Х              | Х              |  | X              | Х                        | L              | R <sub>1</sub> | R <sub>2</sub> | $R_3$  |                | R <sub>8</sub>   |                 |                |                |                |                |                |

|               |       | P,                      | P <sub>2</sub> | P <sub>3</sub> |  | P <sub>8</sub> | P <sub>8</sub>           | H              | P <sub>1</sub> | P <sub>2</sub> | Рз     |                | P <sub>8</sub>   | L               | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> |                | P <sub>8</sub> |

|               |       |                         |                |                |  |                |                          |                | Х              | Χ              | Х      |                | X                | H               | Н              | Н              | Н              |                | Н              |

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State