# NuDAQ<sup>â</sup>

# ACL-7122

144-bit Digital I/O Card

User's Guide

@Copyright 1995~2000 ADLINK Technology Inc. All Rights Reserved.

Manual Rev. 3.50: September 5, 2000

The information in this document is subject to change without prior notice in order to improve reliability, design and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### Trademarks

NuDAQ, ACL-LVIEW are trademarks of ADLINK Technology Inc.

Other product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

# **Table of Contents**

| How to Use This Manualii                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 Introduction1                                                                                                                                                                                                              |

| 1.1Features                                                                                                                                                                                                                          |

| Chapter 2 Installation4                                                                                                                                                                                                              |

| 2.1What You Have42.2Unpacking42.3PCB Layout52.4Jumper and DIP Switch Description62.5DIO Numbers Setting62.6Base Address Setting62.7Interrupt Setting82.8Connector Pin Assignment102.9Connection112.10Software Library Installation12 |

| Chapter 3 Registers Format14                                                                                                                                                                                                         |

| 3.1       Registers Map       14         3.2       Mode 0 of 8255 PPI       15         3.3       Interrupt Handling       16         3.4       Programming Notes       17         3.5       Programming in C language       18       |

| Product Warranty/Service21                                                                                                                                                                                                           |

# How to Use This Manual

This manual is designed to help you use the ACL-7122. The manual describes how to modify various settings on the ACL-7122 card to meet your requirements. It is divided into three chapters:

- Chapter 1, "Introduction," gives an overview of the product features, applications, and specifications.

- Chapter 2, "Installation," describes how to install the ACL-7122. The layout of ACL-7122 is shown, the DIP switch setting for base address, and jumpers setting for IRQ level and interrupt status are specified.

- Chapter 3, "Registers Format," describes the registers format and how to program the digital input / output channels on the ACL-7122.

# 1

# Introduction

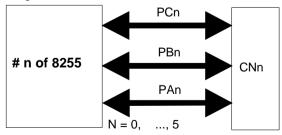

The ACL-7122 is a 144-channel high-density parallel digital I/O board for ISA bus. This board provides 6 sets of 24-channel I/O interface. Every 24-channel interface are to emulate mode 1 of the industry standard 8255 Programmable Peripheral Interface (PPI) chips, each offers three 8-bit ports: PA, PB, and PC. PC is subdivided into 2 nibble-wide (4-bit) ports. Each channel has an individual connector with OPTO-22 pin assignment.

## 1.1 Features

The ACL-7122 144-Bit Parallel Digital I/O Board provides the following advanced features:

- Compact size (suitable for any size of chassis)

- 144 TTL/DTL compatible digital I/O lines

- Emulates six industry standard mode 0 of 8255 PPI

- Buffered circuits for higher driving

- Direct interface with OPTO-22 compatible I/O module

- Programmable interrupt sources

- Output status read-back

- Fully hardware and software compatible with Advantech PCL-722

# 1.2 Applications

- High-density programmable mixed digital input & output

- Industrial monitoring and control

- Digital I/O control

- Contact closure, switch/keyboard monitoring

- Connects with OPTO-22 compatible modules

# 1.3 Specifications

#### " Digital I/O ( DIO)

- Number of channels: 144 TTL digital compatible inputs and outputs

- Input Voltage:

Logic High Voltage: Min. 2.0V, Max. 5.25V Logic Low Voltage: Min 0.0V, Max. 0.8V Logic High Current: 22.0 uA @ 5V Logic Low Current: -0.2 mA @ 0V

- Output Voltage: (Port A and Port B) Logic High Voltage: Min. 2.4 V Logic Low Voltage: Max. 0.5V Logic High Current: -2.6 mA (current source) Logic Low Current: 24.0 mA (current sink)

- Output Voltage: (Port C) Logic High Voltage: Min. 2.4 V Logic Low Voltage: Max. 0.5V Logic High Current: -15.0 mA (current source) Logic Low Current: 24.0 mA (current sink)

- " General Specifications

- I/O Base Address: 16 consecutive address location

- Interrupt IRQ: IRQ 3,5,6,7,9,10,11,12,15 (jumper selectable)

- Connector: six 50-pin male ribbon cable connectors

- Operating Temperature: 0° C ~ 55° C

- Storage Temperature: -20° C ~ 80° C

- Humidity: 5 ~ 95%, non-condensing

- Power Consumption: +5 V @ 1.4A typical, 1.8A maximum

- Dimension: 183 mm (L) X 119 mm

# 1.4 Software Supporting

The ACL-7122 is programmed using simple 8-bit I/O port commands. Users can use high level language, such as BASIC, C, or PASCAL, or low-level language, such as assembly to program the board. For the programming under Windows or LabView, we provide ACLS-DLL1 or ACLS-LVIEW whish is not free of charge. Please contact your dealer to purchase them, then you can get the serial number for installing the ACLS-DLL1 and ACLS-LVIEW. Without the serial number, you can still install the software drivers, however, your applications is with limitation that run only two hours.

### 1.4.1 ACLS-DLL1

For easily program the board under Windows environment, we also provide ACLS-DLL1, which include the DLL for Windows 95/98/NT. With ACLS-DLL1, you can use compilers such as VB, VC/C++, or Delphi.

#### 1.4.2 ACLS-LVIEW

For easily link the ACL-7122 with LabView of National Instrument, the ACLS-LVIEW includes the Vis of the ACL-7122 under for Windows 3.1/95/98 and NT.

# 2

# Installation

This chapter describes how to install the ACL-7122. The following procedures show the installation procedures:

- 1. Check what you have

- 2. Check the PCB and check the location of jumper and switch

- 3. Setup the jumpers according to the operation theorem

- 4. Installation the DOS software library if necessary

## 2.1 What You Have

In addition to this manual, the package includes the following items:

- ACL-7122 144-bit Digital I/O Card

- ADLINK CD

If any of these items is missing or damaged, contact the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

# 2.2 Unpacking

Your ACL-7122 card contains sensitive electronic components that can be easily damaged by static electricity.

The card should be done on a grounded anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the card module carton for obvious damage. Shipping and handling may cause damage to your module. Be sure there are no shipping and handling damages on the module before processing.

After opening the card module carton, exact the system module and place it only on a grounded anti-static surface component side up.

Again inspect the module for damage. Press down on all the socketed IC's to make sure that they are properly seated. Do this only with the module place on a firm flat surface.

Note : DO NOT APPLY POWER TO THE CARD IF IT HAS BEEN DAMAGED.

You are now ready to install your ACL-7122.

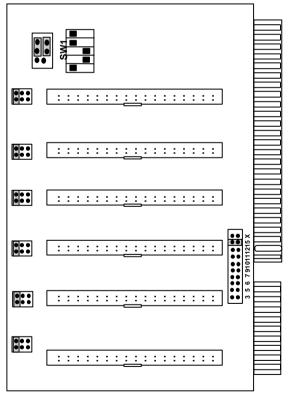

# 2.3 PCB Layout

Figure 2.1

# 2.4 Jumper and DIP Switch Description

You can change the ACL-7122's base address, address parameters, and interrupt by setting DIP switches and jumpers on the card. The card's jumpers and switches are preset at the factory. Under normal circumstances, you should not need to change the jumper settings.

A jumper switch is closed (sometimes referred to as "shorted" with the plastic cap inserted over two pins of the jumper). A jumper is open with the plastic cap inserted over one or no pin(s) of the jumper.

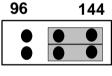

# 2.5 DIO Numbers Setting

The ACL-7122 can provide two I/O capability modes: 144-bit and 96-bit. The modes are selected by switch **SW2** (see the figure below). The 144-bit mode requires 32 consecutive I/O address. The 96-bit mode just occupies 16 address ports. The default setting of the ACL-7122 is set as 144-bit mode. The 96-bit is used only when the address conflicts with address of other I/O cards.

SW2

Note: In 96-bit mode, two or more boards can be mapped consecutively on adjacent addresses. But, the 144-bit mode, each board should have a gap of 8 addresses.

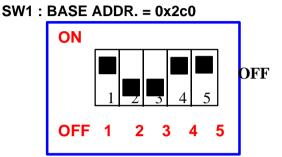

## 2.6 Base Address Setting

The ACL-7122 requires 32 or 16 consecutive address locations in I/O address space. The base address of the ACL-7122 is restricted by the following conditions.

- 1. The base address must be within the range 200hex to 3FFhex.

- 2. The base address should not conflict with any PC reserved I/O address or other I/O cards' address.

The ACL-7122 requires 32 consecutive address locations for 144-bit mode, or 16 address locations for 96-bit mode. The I/O port base address is selectable by a 5 position DIP switch SW1 (refer to Figure 2.3). The address setting of 144-bit mode for I/O port from hex200 to hex3FE is described in Table 2.2. The address setting of 96-bit mode is described in Table 2.3.

Figure 2.3 Default Switch Setting

| I/O port                        | 1          | 2          | 3          | 4          | 5  |

|---------------------------------|------------|------------|------------|------------|----|

| address(hex)                    | A8         | A7         | A6         | A5         | A4 |

| 200-21F                         | ON<br>(0)  | ON<br>(0)  | ON<br>(0)  | ON<br>(0)  | Х  |

| :                               |            |            |            |            |    |

| (*) 2C0-2DF<br>(default seting) | ON<br>(0)  | OFF<br>(1) | OFF<br>(1) | ON<br>(0)  | Х  |

| :                               |            |            |            |            |    |

| 380-29F                         | OFF<br>(1) | OFF<br>(1) | OFF<br>(1) | ON<br>(0)  | Х  |

| 3A0-3BF                         | OFF<br>(1) | OFF<br>(1) | OFF<br>(1) | OFF<br>(1) | Х  |

| 3C0-3DF                         | OFF<br>(1) | OFF<br>(1) | OFF<br>(1) | ON<br>(0)  | Х  |

| 3E0-3FF                         | OFF<br>(1) | OFF<br>(1) | OFF<br>(1) | OFF<br>(1) | Х  |

X : Don't care, ON = 0; OFF = 1

A2, ..., A8 are corresponding to address lines of ISA bus. A9 is always  ${\bf 1}$  (OFF).

Table 2.2 144-bit mode

Note: In 144-bit mode, the base address line A4 is don't cared.

| A8  | 2<br>A7                      | 3<br>A6                                                    | 4<br>A5                                                                       | 5<br>A4                                                                    |

|-----|------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| ON  | ON                           | ON                                                         | ON                                                                            | ON                                                                         |

|     |                              |                                                            |                                                                               |                                                                            |

| ON  | OFF                          | ON                                                         | ON                                                                            | OFF                                                                        |

| ON  | OFF                          | ON                                                         | OFF                                                                           | ON                                                                         |

|     |                              |                                                            |                                                                               |                                                                            |

| OFF | OFF                          | OFF                                                        | ON                                                                            | OFF                                                                        |

| OFF | OFF                          | OFF                                                        | OFF                                                                           | ON                                                                         |

| OFF | OFF                          | OFF                                                        | OFF                                                                           | OFF                                                                        |

|     | ON<br>ON<br>ON<br>OFF<br>OFF | ON ON<br>ON OFF<br>ON OFF<br>OFF OFF<br>OFF OFF<br>OFF OFF | ON ON ON<br>ON OFF ON<br>ON OFF ON<br>ON OFF ON<br>OFF OFF OFF<br>OFF OFF OFF | ONONONONONOFFONONONOFFONOFFONOFFOFFOFFOFFOFFOFFOFFOFFOFFOFFOFFOFFOFFOFFOFF |

Table 2.3 96-bit mode

#### How to Define a Base Address for the ACL-7122 ?

The DIP1 to DIP6 in the switch SW1 are one to one corresponding to the PC bus address line A9 to A4. A9 is always 1; A3 to A0 are always 0 with hardware. If you want to change the base address, you can only change the values of A8 to A4 (shadow area of below diagram). Following is an example, which shows you how to define the base address as **Hex 2C0**.

#### Base Address: Hex 2C0

| 2   |    | <u>C</u> |     |    |    | <u>0</u> |    |    |    |

|-----|----|----------|-----|----|----|----------|----|----|----|

| 1   | 0  | 1        | 1   | 0  | 0  | 0        | 0  | 0  | 0  |

| A9  | A8 | A7       | A6  | A5 | A4 | A3       | A2 | A1 | A0 |

| OFF | ON | OFF      | OFF | ON | ON |          |    |    |    |

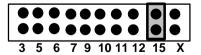

## 2.7 Interrupt Setting

The ACL-7122 provides 9 interrupt requests levels (IRQ) 3, 5, 6, 7, 9, 10, 11, 12 and 15. The IRQ level is set by jumper JP6. The IRQ signal is Tristate allowing multiple ACL-7122 boards to share the same interrupt line. For example, two ACL-7122 can share IRQ 3 in one system.

JP6 (Default setting IRQ15)

The ACL-7122 has two lines (PC0 and PC3) to generate hardware

interrupt. The interrupt are edge-triggered, PC0 traps a rising edge signal, which PC3 traps a falling edge signal.

To use the interrupt, first you have to select the desired IRQ interrupt level. For determining which input to generate the interrupt, you can read Port C, bit PC-0 and bit PC-3, to locate the current state of inputs.

**Note:** Input is not latched and no first event trapping is provided to determine which input was active first.

There are six jumpers from JP0 to JP5, which are corresponding to each channel in ACL-7122, for interrupt enabled selection. The figure 2.3 below shows three status of interrupt setting for CH3.

D: Disabled Interrupt - No interrupt request

- P: Programmable Interrupt interrupt when CH3's PC4 is "Low"

- E: Enable Interrupt interrupts request

#### A Summary of Interrupt Status

In ACL-7122, the interrupt trigger source is depended on jumper J0 to J5, and, I/O lines, PC0, PC3 and PC4. All the possibility of interrupt statuses are shown in the following table.

| JPn( n=05)               | PC0  | PC3    | PC4 | Interrupt Status     |

|--------------------------|------|--------|-----|----------------------|

| D<br>P<br>E<br>••<br>JPn | x    | х      | x   | No Interrupt Request |

|                          | LOW  | L -> H | LOW |                      |

| D ●●<br>P ●● JPn<br>E ●● | L->H | HIGH   | LOW | Interrupt Request    |

|                          | HIGH        | Х              | LOW  | No Interrupt Deguest |

|--------------------------|-------------|----------------|------|----------------------|

| P<br>E<br>E              | х           | LOW            | LOW  | No Interrupt Request |

| D<br>P<br>E<br>••<br>JPn | х           | х              | HIGH | No Interrupt Request |

| D<br>P<br>E              | HIGH<br>X   | X<br>LOW       | x    | No Interrupt Request |

| D<br>P<br>E              | LOW<br>L->H | L -> H<br>HIGH | х    | Interrupt Request    |

X : Don't Care

H-> L : Rising Edge Trigger ( from High to Low)

L->H : Falling Edge Trigger ( from Low to High)

# 2.8 Connector Pin Assignment

The I/O ports of ACL-7122 emulate six mode 0 of Intel 8255 general purpose programmable peripheral interface. Figure 2.4 shows ACL-7122's equally block diagram of each channel. There are six 50-pin connectors come equipped with the ACL-7122 board, and each of them is corresponding to a mode 0 of 8255. The connector pin assignment is specified in Figure 2.5.

Figure 2.4 Block Diagram of Each Channel

|           |    |    | 1   |

|-----------|----|----|-----|

| Port C D7 | 1  | 2  | GND |

| Port C D6 | 3  | 4  | GND |

| Port C D5 | 5  | 6  | GND |

| Port C D4 | 7  | 8  | GND |

| Port C D3 | 9  | 10 | GND |

| Port C D2 | 11 | 12 | GND |

| Port C D1 | 13 | 14 | GND |

| Port C D0 | 15 | 16 | GND |

| Port B D7 | 17 | 18 | GND |

| Port B D6 | 19 | 20 | GND |

| Port B D5 | 21 | 22 | GND |

| Port B D4 | 23 | 24 | GND |

| Port B D3 | 25 | 26 | GND |

| Port B D2 | 27 | 28 | GND |

| Port B D1 | 29 | 30 | GND |

| Port B D0 | 31 | 32 | GND |

| Port A D7 | 33 | 34 | GND |

| Port A D6 | 35 | 36 | GND |

| Port A D5 | 37 | 38 | GND |

| Port A D4 | 39 | 40 | GND |

| Port A D3 | 41 | 42 | GND |

| Port A D2 | 43 | 44 | GND |

| Port A D1 | 45 | 46 | GND |

| Port A D0 | 47 | 48 | GND |

| +5V       | 49 | 50 | GND |

|           |    |    |     |

Figure 2.5 Connector Pin Assignment

## 2.9 Connection

There are three daughter boards to connect with ACL-7122 for DIO operation. The following diagrams show you how to configuration your ACL-7122 with different terminal boards.

#### 1. TB-24R, DIN-24R

The TB-24R and DIN-24R provide 24 Form C relays for digital output control. The connection between ACL-7122 and TB-24R is:

### 2. TB-24 P, DIN-24P

The TB-24P and DIN-24P provide 24 opto-isolated digital input channels, the connection between ACL-7122 and TB-24P is:

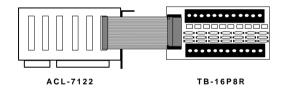

### 3. TB-16P8R

The TB-16P8R provides 16 opto-isolated digital input channels and 8 relay outputs, the connection between ACL-7122 and TB-16P8R is:

# 2.10 Software Library Installation

This section describes the DOS software library, which is free supplied. The function prototypes and some useful constants are defined in the header files in LIB directory. The DOS library software includes a utility program, C language library, and some demonstration programs, which can help you reduce the programming work. Please refer to the ACLS-DLL1 function reference manual, which included in ADLINK CD. The DOS functions are compatible with ACLS-DLL1 functions except without "W" prefix in function names.

To program in Windows environment, please use ACLS-DLL1 which needs license.

To install the DOS library software and utilities, please follow the following installation procedures:

- 1. Put ADLINK CD into the appropriate CD-ROM drive.

- Type the following commands to change to the card's directory (X indicates the CD-ROM drive): X:>CD \NuDAQISA\7122

- **3.** Execute the setup batch program to install the software: *X*:\NuDAQISA\7122>**SETUP**

After installation, all the files of ACL-7122 Library & Utility for DOS are stored in C:\ADLINK\7122\DOS sub-directory.

# 3

# **Registers Format**

# 3.1 Registers Map

The ACL-7122 needs 24 bytes of I/O address to operate. The relationship of I/O address and ports' data read / write shows as following table, the default base address of below table is 2C0H.

| PORT SELECT      | ADDR. | NOTE            |

|------------------|-------|-----------------|

| CH0 PA0          | 2C0H  | EMULATE 8255 PA |

| CH0 PB0          | 2C1H  | EMULATE 8255 PB |

| CH0 PC0          | 2C2H  | EMULATE 8255 PC |

| CONTROL WORD CH0 | 2C3H  | EMULATE 8255 CW |

| CH1 PA1          | 2C4H  | EMULATE 8255 PA |

| CH1 PB1          | 2C5H  | EMULATE 8255 PB |

| CH1 PC1          | 2C6H  | EMULATE 8255 PC |

| CONTROL WORD CH1 | 2C7H  | EMULATE 8255 CW |

| CH2 PA2          | 2C8H  | EMULATE 8255 PA |

| CH2 PB2          | 2C9H  | EMULATE 8255 PB |

| CH2 PC2          | 2CAH  | EMULATE 8255 PC |

| CONTROL WORD CH2 | 2CBH  | EMULATE 8255 CW |

| CH3 PA3          | 2CCH  | EMULATE 8255 PA |

| CH3 PB3          | 2CDH  | EMULATE 8255 PB |

| CH3 PC3          | 2CEH  | EMULATE 8255 PC |

| CONTROL WORD CH3 | 2CFH  | EMULATE 8255 CW |

| CH4 PA4          | 2D0H  | EMULATE 8255 PA |

| CH4 PB4          | 2D1H  | EMULATE 8255 PB |

| CH4 PC4          | 2D2H  | EMULATE 8255 PC |

| CONTROL WORD CH4 | 2D3H  | EMULATE 8255 CW |

| n                |      |                      |

|------------------|------|----------------------|

| CH5 PA5          | 2D4H | EMULATE 8255 PA      |

| CH5 PB5          | 2D5H | EMULATE 8255 PB      |

| CH5 PC5          | 2D6H | EMULATE 8255 PC      |

| CONTROL WORD CH5 | 2D7H | EMULATE 8255 CW      |

|                  | 2D8H | Reserved by ACL-7122 |

|                  | 2D9H | Reserved by ACL-7122 |

|                  | 2DAH | Reserved by ACL-7122 |

|                  | 2DBH | Reserved by ACL-7122 |

|                  | 2DCH | Reserved by ACL-7122 |

|                  | 2DDH | Reserved by ACL-7122 |

|                  | 2DEH | Reserved by ACL-7122 |

|                  | 2DFH | Reserved by ACL-7122 |

Table 4.2 Ports' I/O Map (Base Address = 2C0H)

# 3.2 Mode 0 of 8255 PPI

The ACL-7122 can emulates MODE 0 of 8255 PPI, and it comes equipped with six 50-pin male IDC connectors that interface with OPTO-22 racks 8, 16, and 24.

The basic function definitions of 8255 mode 0 are:

- Two 8-bit I/O ports PA and PB

- Two nibble-wide (4-bit) ports PC upper and PC lower

- Any ports can be used for both input and output

- Outputs are latched whereas inputs are not latched

Two of the I/O lines (PC-0, PC-3) of each channel can be used to generate a hardware interrupt.

The control word is used to program PA, PB and PC as input port or output port. The following table summarizes the control word (D0 - D4) and the corresponding mode state (Mode 0 - Mode 15).

| Mode | Config.<br>Value | D4 | D3 | D1 | D0 | PORT<br>A | PORT C<br>UPPER | PORT<br>B | PORT C<br>LOWER |

|------|------------------|----|----|----|----|-----------|-----------------|-----------|-----------------|

| 0    | 80H              | 0  | 0  | 0  | 0  | O/P       | O/P             | O/P       | O/P             |

| 1    | 81H              | 0  | 0  | 0  | 1  | O/P       | O/P             | O/P       | I/P             |

| 2    | 82H              | 0  | 0  | 1  | 0  | O/P       | O/P             | I/P       | O/P             |

| 3    | 83H              | 0  | 0  | 1  | 1  | O/P       | O/P             | I/P       | I/P             |

| 4    | 88H              | 0  | 1  | 0  | 0  | O/P       | I/P             | O/P       | O/P             |

| 5    | 89H              | 0  | 1  | 0  | 1  | O/P       | I/P             | O/P       | I/P             |

| 6    | 8AH              | 0  | 1  | 1  | 0  | O/P       | I/P             | I/P       | O/P             |

| 7    | 8BH              | 0  | 1  | 1  | 1  | O/P       | I/P             | I/P       | I/P             |

| 8    | 90H              | 1  | 0  | 0  | 0  | I/P       | O/P             | O/P       | O/P             |

| 9    | 91H              | 1  | 0  | 0  | 1  | I/P       | O/P             | O/P       | I/P             |

| 10   | 92H              | 1  | 0  | 1  | 0  | I/P       | O/P             | I/P       | O/P             |

| 11   | 93H              | 1  | 0  | 1  | 1  | I/P       | O/P             | I/P       | I/P             |

| 12   | 98H              | 1  | 1  | 0  | 0  | I/P       | I/P             | O/P       | O/P             |

| 13   | 99H              | 1  | 1  | 0  | 1  | I/P       | I/P             | O/P       | I/P             |

| 14   | 9AH              | 1  | 1  | 1  | 0  | I/P       | I/P             | I/P       | O/P             |

| 15   | 9BH              | 1  | 1  | 1  | 1  | I/P       | I/P             | I/P       | I/P             |

Table 4.1 Summarize of control word (D0 - D4) and mode state (Mode 0 - Mode 15)

# 3.3 Interrupt Handling

The ACL-7122 can generate a hardware interrupt to your PC. The following issues should be careful when you want to generate an interrupt trigger.

- 1. Interrupt IRQ level setting: make sure you already set the right IRQ level by using the jumper J6.

- 2. Interrupt trigger status setting:

- **a.** interrupt mode: make sure the jumper J2 is already set as *E*(*Enable*) or *P*(*PMG*) mode.

- **b.** interrupt trigger edge: if you choose E mode, be careful the following combinations of PC-0 and PC-3:

| PC0              | PC3         | Status               |

|------------------|-------------|----------------------|

| High             | Х           | No Interrupt Request |

| Low              | Low >> High | Interrupt Request    |

| Х                | Low         | No Interrupt Request |

| Low >> High      | High        | Interrupt Request    |

| (X) : Don't care |             |                      |

c. Programmable mode: if you choice P mode, confirm the, I/O line, PC-4 is kept in TTL LOW status. Otherwise, there is no

interrupt trigger will be occurred. The relationship between PC4, PC3 and PC0 is :

| PC4  | PC0         | PC3         | Status               |

|------|-------------|-------------|----------------------|

|      | High        | Х           | No Interrupt Request |

|      | Low         | Low >> High | Interrupt Request    |

| Low  | Х           | Low         | No Interrupt Request |

|      | Low >> High | High        | Interrupt Request    |

| High | Х           | Х           | No Interrupt Request |

(X) : Don't care

**Note** : Since the ACL-7122's Input is not latched and no first event trapping is provided to determine which input was active first.

#### Self Interrupt Trigger

Although the ACL-7122's interrupt signals are normal received from external peripherals. It can also generate a test output signal to emulate an interrupt being inputted from an external device.

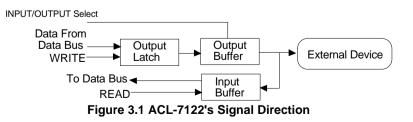

## 3.4 Programming Notes

Before programming the ACL-7122, the following notes will help you are more skillful to control the I/O operations through the ACL-7122.

#### 1. Default Input Mode

After power-on or hardware reset your PC system, all the ports of ACL-7122 are automatically configured as *INPUT* mode.

#### 2. Output Latch

When an output port is programmed as output mode through control word, it will not affect the connected output device until an output instruction is executed. This means the data will not output until execute the first output instruction.

- 3. According the above ACL-7122's signal direction block diagram, some issues should be careful.

- a. When a port is set as INPUT or after hardware RESET, its output buffer is *Disabled* (high impedance)

- **b.** The output data is lactated in the *Output Latch* when it is set as OUTPUT mode.

- **c.** When the port is set as OUTPUT, the input circuit is used as an output status read-back.

- **d.** The data in Output Latch is an random value after power on. It has to be initialized before the port to output direction.

# 3.5 Programming in C language

The following parts are example programs written in C language. The first four parts are just partial programs for your reference; you can not compile them before these programs are complete.

The last program is an example for interrupt handling, you could compile it by Borland C/C++ compiler directly.

#### 1. To initial I/O port

```

# define BASE 0x2C0 //define base address

# define CWD0 0x80 //XX refer to 8255 CW

int i;

for( i = 0 ; i < 6; i++)

{

outportb( BASE + i * 4 + 0 , 0x00);

outportb( BASE + i * 4 + 1 , 0x00);

outportb( BASE + i * 4 + 2 , 0x00);

outportb( BASE + i * 4 + 3 , CWD);

/* all as output */

}

2. To write port</pre>

```

```

# define BASE 0x2C0 //define base address

# define PA 0x0 // Port A

# define PB 0x1 // Port B

# define PC 0x2 // Port C

# define CWD 0x80 //ALL output to 8255 CW

outportb(BASE + 3,CWD); //index to CH0 CW

outportb(BASE + PA ,0x23);// write 23H to CH0 PA

outportb(BASE + PB ,0x45);// write 45H to CH0 PA

outportb(BASE + PC ,0xfd);// write fdH to CH0 PA

```

#### 3. To access port

```

# define BASE 0x2C0

//define base address

# define PA

0 \times 0

// Port A

# define PB

// Port B

0x1

# define PC

// Port C

0x2

# define CWD 0x9B

//ALL input from 8255 CW

int pa_data, pb_data, pc_data;

outportb(BASE + 3,CWD);

//index to CH0 CW

```

```

pa_d = inportb(BASE + PA); // read from CH0 PA

pb_d = inportb(BASE + PB); // read from CH0 PB

pc_d = inportb(BASE + PC); // read from CH0 PC

```

#### 4. To clear and enable interrupt

```

# define INDEX 0x2C0 //INDEX same as SW

//setting

# define DATAS 0x301 //data R/W port

# define CW1 0x3 //8255 port 0 CW index

int dummy; //dummy data buffer

outportb(INDEX,CW1); //index to CW

dummy = inportb(DATA); //dummy read to clear

//and enable interrupt

```

#### 5. A Complete Example Program for Interrupt Handling

```

This program deno. how to generate interrupt by *

* the ACL-7122 itself. When you press any key, a

* beep is generated. When you press ESC key, the *

system will be quit.

* Hardware setting :

Base Address : 0x2C0

IRQ Level : 9 (Jumper J6)

Int mode : P (jumper J0)

*

*

edge trigger : PC3 0->1 ( rising edge)

#include <stdio.h>

#include <dos.h>

#include <conio.h>

#define IRO2

0x0a

#define EOI

0 \times 20

#define BASE_ADDR 0x2c0

#define PA

0 \times 00

```

```

#define PB

0 \times 01

#define PC

0 \times 02

#define CW

0x03

void interrupt isr_7122()

{

printf("7");

// beep

outportb( 0x20, EOI); // EOI of 8259

}

main()

{

int mask, keyin;

void interrupt (*old_irq2_isr)();

old_irq2_isr = getvect( IRQ2);

setvect( IRQ2, isr_7122);

mask = inportb( 0x21);

outportb( BASE_ADDR + CW, 0x80); // set PA, PB and PC

// as output mode

clrscr();

// clear screen

printf( " press <ESC> to QUIT \n");

do

{

keyin = 0;

printf(" press any key to genetate an interrupt

except <ESC>\n");

keyin = bioskey(0);

outportb( 0x21, 0xbf & mask); // IRQ2 nonmasked

outportb( BASE_ADDR + PC, 0x00);

delay( 100);

outportb( BASE_ADDR + PC, 0x08);

} while( (keyin & 0xff) != 27); // QUIT when ESC

pressed

setvect( IRQ2, old_irq2_isr); // restore old isr

outportb( 0x21, mask);

// restore 8259 mask}

```

# **Product Warranty/Service**

Seller warrants that equipment furnished will be free form defects in material and workmanship for a period of one year from the confirmed date of purchase of the original buyer and that upon written notice of any such defect, Seller will, at its option, repair or replace the defective item under the terms of this warranty, subject to the provisions and specific exclusions listed herein.

This warranty shall not apply to equipment that has been previously repaired or altered outside our plant in any way as to, in the judgment of the manufacturer, affect its reliability. Nor will it apply if the equipment has been used in a manner exceeding its specifications or if the serial number has been removed.

Seller does not assume any liability for consequential damages as a result from our products uses, and in any event our liability shall not exceed the original selling price of the equipment.

The equipment warranty shall constitute the sole and exclusive remedy of any Buyer of Seller equipment and the sole and exclusive liability of the Seller, its successors or assigns, in connection with equipment purchased and in lieu of all other warranties expressed implied or statutory, including, but not limited to, any implied warranty of merchant ability or fitness and all other obligations or liabilities of seller, its successors or assigns.

The equipment must be returned postage-prepaid. Package it securely and insure it. You will be charged for parts and labor if you lack proof of date of purchase, or if the warranty period is expired.